If you’re building a dev board for your project or using a common MCU, you’ll find many protocols for communicating other active components. Standards like USB and Ethernet are built into most controllers for working with computer peripherals. Still, protocols like I2C, SPI, UART, and others are used to interface with downstream MCUs or programmable ICs. The differences between I2C vs. SPI vs. UART buses are simple, and any designer working with an MCU should know how to set up routing and layout for these protocols.

Altium TechDocs are online documentation for Altium products, providing the basic information you need to get the most out of our tools. Discover features you didn't know existed and get the most out of those you already know about. Dual boot system, allowing the board to update its firmware in the field by itself, over a standard USB connection. 4x Relay and Power PWM drivers; USB Hub, providing for the connection of up to three USB devices to be attached for use by an FPGA design programmed within the User FPGA. Click the button below to download the latest Altium. If this driver doesn't work, I show the steps to download and install the latest FTDI USB drivers. In case you are wondering, FTDI is a company that develops integrated circuits to enable standard serial communication through the USB port. The MCP2200 USB to UART with Isolation Demo Board is a USB to UART development and evaluation board for the MCP2200 device. This board is powered from the host’s USB port. Two of the MCP2200 GPIO pins (GP6 and GP7) are connected to LEDs used to indicate the USB to UART traffic when the associated pins are configured as TxLED and RxLED pins.

Because there is a lot of libraries I have done, I will make a table with all of my libraries at one place. When new library will be created, it will be posted here. These libraries work on both Discovery boards, if not, it will be specified. Actually, libraries should work on STM32F4xx series of microcontrollers if they have peripherals that are need for library. All STM32F4xx MCUs don’t.

These protocols are slower speed signaling standards, so you almost always won’t need to worry about things like impedance control or transmission line behavior if you are working with these protocols. However, some important design points must be considered when ensuring your bus lines’ signals are read correctly at your receivers. There is also the matter of addressing, but the particular product and your code can handle this point. For now, let’s look at how these three common protocols can be used in your PCB layout and some important points to maintain signal integrity.

Differences Between I2C vs. SPI vs. UART

Everything from 8-bit to 32-bit MCUs will use at least one of these protocols alongside GPIOs for programmability and sending signals to simple peripherals. These three serial protocols are bus protocols; I2C and UART use addressing schemes, while SPI is address-less. Although SPI is address-less, it is a bus protocol and can still be used to select downstream devices to receive data.

I2C Protocol

I2C (pronounced I-squared C, or sometimes IIC for inter-integrated circuit) uses two lines (standard, fast, and fast-plus modes) to control other devices; one line is a clock line (SCL), while the other is a data line (SDA). It comes in three modes, which are summarized in the table below. Note that the rise/fall time values assume the typical series resistors are installed at the I/Os.

Mode | Data rate/clock speed | Max. rise/fall time | Min. rise/fall time | Directionality |

Standard | 100 kHz | 1000 ns | - | Bidirectional |

Fast | 400 kHz | 300 ns | 20 ns* | Bidirectional |

Fast-plus | 1 MHz | 300 ns | 20 ns* | Bidirectional |

High speed | 3.4 MHz (100 pF bus) 1.7 MHz (400 pF bus) | 120 ns** | 15 ns** | Bidirectional |

Ultra-fast | 5 MHz | 50 ns | 25 ns | Unidirectional |

*Assumes VDD/VCC = 5.5 V. Scales down linearly if VDD/VCC is lower

**Divide these values by 2 for the clock line

Note that ultra-fast mode is the only mode where communication is used for downstream write operations only. This mode is also important as it helps us see when the bus impedance will need to be matched, which in practical terms is almost never. If we take a very conservative 10% limit on the critical line length, we find that the crucial length in these lines is 0.32 m, which is much longer than the size of most boards that will use I2C. If we use the knee frequency for the minimum rise/fall time with a 10% limit on critical length, we come to a much longer value of 0.92 m. We should take the more conservative number of 0.32 m for ultra-fast mode; any I2C line shorter than this value will not behave as a transmission line, and we only need to worry about the termination scheme.

The important points in termination are to select the right pull-up and series resistors. The pull-up resistors and the capacitance of the VDD/VCC line bus form a discharging and charging RC circuit, which is what provides a signal to the receiver when the driver switches. The pull-up resistor values (Rp) for the signal and clock lines must obey the following inequality:

The bus capacitance is determined using the standard formulas for the VCC bus impedance, which is calculated using the same equations you would use for a transmission line (either microstrip or stripline). You can then solve for the bus capacitance using the impedance and the propagation delay for the line. The series resistors are optional under the I2C standard, although they can be included to protect the devices from voltage spikes and slow down the rise/fall times. Look at page 59 of the I2C standard to determine the right series resistor value to pair with your pull-up resistor value.

SPI Protocol

The SPI protocol is similar to I2C. A total of 4 lines are used in this bus, and components can be arranged in two possible modes. If a single controller device is used to trigger a single downstream device, the topology is simply point-to-point. Triggering multiple devices depends on the number of chip-select outputs provided by the driver (standard mode). The second mode uses daisy-chaining, where a single device-select output successively triggers each device in the daisy chain.

Unlike I2C, the various signaling parameters in SPI are highly configurable. Unless you are running an extremely fast interface, you can approximate the signal level across the interconnect as DC as you’ll be below the critical length for transmission line behavior. You can then use a series resistor to terminate the driver’s low impedance output and ensure maximum power transfer. The RC discharging method with the trace capacitance shown above can control the output current and rise/fall times from your interface.

UART Protocol

The universal asynchronous receiver-transmitter (UART) is similar to I2C. These interfaces have a maximum data rate of ~5 Mbps. UART devices are also easy to work with as there is no clock sent between devices; everything is asynchronous. Note that each UART device’s internal (system) clock must run at some multiple of the baud rate (i.e., each bit is sampled N times). Only two wires are used for communication between a single controller device and a single downstream device.

Note that the data format, signal levels, and baud rate of a UART device are configurable with an external driver circuit. Unfortunately, this also means there are few hard and fast rules for routing and layout of UART devices. Follow the standard high-speed design guidelines for determining when termination is needed by looking at the transition to transmission line behavior (see the article I linked above). A typical termination method to reduce overshoot is a series termination. Note that UART may idle at high or low levels, and pull-up resistors may be needed to set the required idle level; be sure to check your component specifications before adding pull-up resistors.

You can read more about the difference between timing in synchronous and asynchronous buses in this 2018 AltiumLive presentation by Max Seeley.

Summary

If SPI and UART rules seem a bit vague, it’s because you have more freedom to design your interface at the firmware level. Once any of these standards run at fast edge rates, they are susceptible to crosstalk, just like high-speed signaling standards. However, because you have plenty of flexibility in your specification, you can usually design traces to have lower inductance and reduce inductive crosstalk. You have some flexibility in routing these signals and making them very easy to work within your next digital system.

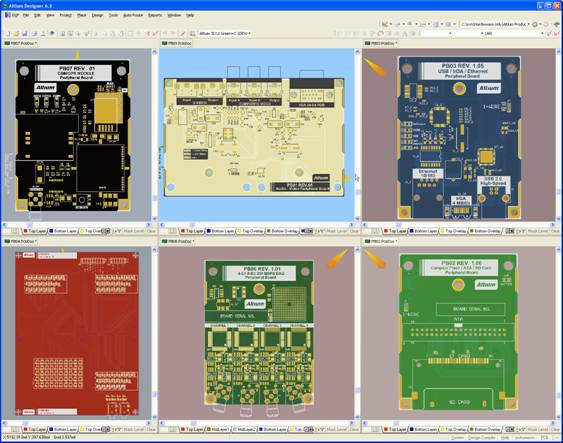

When designing digital systems with common signaling standards, you can design for the differences between I2C vs. SPI vs. UART with the design rules in Altium Designer®. The Layer Stack Manager and the integrated 3D field solver from Simberian uses your board geometry and trace geometry to extract your bus capacitance and parasitics in your signal lines.

Altium Designer on Altium 365 delivers an unprecedented amount of integration to the electronics industry until now relegated to the world of software development, allowing designers to work from home and reach unprecedented levels of efficiency.

We have only scratched the surface of what is possible to do with Altium Designer on Altium 365. You can check the product page for a more in-depth feature description or one of the On-Demand Webinars.

The FrontPanel SDK dramatically accelerates the development of your FPGA-based USB or PCI Express device by providing three essential components:

Software API and a robust driver to communicate with your device over USB or PCI Express.

Device firmware to manage FPGA configuration and communication.

Small FPGA IP blocks that integrate with your HDL to make host communication simple and easy.

Multi-Platform FrontPanel API and USB Driver

Our robust USB driver and FrontPanel API work together to provide an easy-to-use software interface to your hardware that is consistent across the Windows (32-/64-bit), Linux (32-/64-bit), and Mac OS X development environments.Our PCI Express driver is available for Windows 32-bit and 64-bit operating systems.

And to make things even easier, we provide pre-built wrappers to the FrontPanel API for C, C#, C++, Python, and Java. And the DLL may be used from any of the huge library of software that support external calling such as Matlab and LabVIEW.

FrontPanel Application

Use our stand-alone FrontPanel Application for FPGA and PLL configuration, XML-based Virtual Control Components, firmware updates, general device setup, and more!

The stand-alone FrontPanel Application lets you quickly and easily define your own graphical user interface that communicates with your hardware. FrontPanel supports many basic user interface elements including:

- LEDs

- Hexadecimal displays

- Sliders

- Checkboxes

- Numerical entry

Interactive FrontPanel XFP Scripting

Bring new life to your FrontPanel XFP descriptions with scripting capabilities.

Attach scripts to FrontPanel components to perform event-based computations based on user-input or FPGA communication over wires, triggers, and pipes.

FrontPanel Scripting makes it easy to add business logic to XFP profiles so you can generate interactive interfaces to your hardware faster without having to implement user interfaces using C++ or Python.

Format outputs for human-readable display.

Perform closed-loop processing.

Atomic HDL Modules

The HDL you build into the FPGA constitutes the interface between your instrument and USB. Integrate our intuitive HDL modules into your design and you have a fast, extensible, and simple conduit between your hardware and your software.

Simulation Models

Save hours of development time by specifically targetting components of your design rather than iterating in the dark. Our HDL simulation models describe the behavioral function of the PC to FPGA interaction and work under Xilinx’s iSim, Modelsim, and other HDL simulators.

Custom Interfaces and Test Hardware

Altium Spi/unio Over Usb Driver Download Windows 10

FPGA technology is used in a wide variety of in-house prototypes and other custom projects. These types of projects benefit from both FrontPanel’s easy-to-use virtual interface components as well as the convenience and predictability of the FrontPanel programmer’s interface.

For Students and Educators

FrontPanel is perfect for use in many classroom settings. It’s flexible ease-of-use encourages exploration and makes it possible for students to realize their experiments and projects faster.

In structured courses, educators can setup template interfaces in FrontPanel XML, easing the student’s learning curve while standardizing the way students interface, debug, and evaluate their assignments. Later, students can write custom XML interfaces or even write C++, Python, or Java applications.

Technical Specifications and Support

Features & Specifications

Altium Spi/Unio Over USB Driver Download

- Windows (USB / PCI) API available as DLL (C/C++), C#, Java, Python libraries

- Mac OS X (USB only) API available as universal dynamic library (C/C++), Java, Ruby, Python libraries

- QNX Neutrino 6.5.0 (USB / PCI) API available as shared-object (please contact sales@opalkelly.com for availability).

- Linux (USB only) API available as shared object (C/C++), Java, Ruby, Python libraries

- Behavioral simulation supported, no back-annotation

- USB 3.0 transfer rates up to 340+ MBps

- USB 2.0 transfer rates up to 38 MBps

- PCIe transfer rates up to 200 MBps

Requirements

- Windows 7, Windows 8.1, Windows 10

- Mac OS X Version 10.10+

- Linux CentOS 6.5 32-/64-bit (x86 and amd64)

- Linux Ubuntu 16.04LTS 32-/64-bit (x86 and amd64)

- Linux – Many other distributions also known to work with libraries from the two official distributions above.

- Linux ARM targets as available and One-Time Ports available for a fee. If you require official support for ARM targets, please contact sales@opalkelly.com.

- Simulation: Compatible with most VHDL/Verilog simulators

- Opal Kelly FrontPanel-supported device

- Xilinx ISE 14.1i or later recommended for building FPGA configuration files (Spartan-6 and earlier)

- Xilinx Vivado recommended for building FPGA configuration files (7-Series and later)

- Altera Quartus 15.0 or later recommended for building FPGA configuration files (Cyclone IV and later)

Altium Spi/unio Over Usb Driver Download 64-bit

Altium Spi/unio Over Usb Driver Downloads

Library